## JRC NRD-535(DG) Improved alignment for ECSS

The ECSS mode of the NRD535 is known for sudden howling when the received signal suffers fading or is weak. The tuning has to be shifted by app. 400Hz to achieve best operation and stability of the ECSS.

The reason for this strange behavior is the non linearity of the VCO (regarding tuning voltage and frequency) in the PLL-IC (IC2) MC14046 on the ECSS Unit.

Acc. to the service manual of the 535(DG), RV1 should be set to 4.5VDC on TP4 when receiving a strong signal (40dBuV). This is in the middle of the tuning range of the PLL but due to the mentioned non linearity it is not the optimum regarding stability when receiving weak signals. A different alignment method is proposed:

Use a signal generator (AM set to 1kHz with 75% modulation) with variable output down to 0.1 uV or use an antenna with a variable attenuator (a simple potentiometer will do this job) and tune in an AM-Station – both ways anywhere in the receiving range of the 535(DG).

## NOW:

- 1. Remove top cover and give the 535(DG) app. 10minutes for a warm-up.

- Tune in the signal generator or the AM-station exactly. It is important, that the signal generator or the received AM-station and the setting of the 535(DG) exactly(!) match; it means better than 10Hz! Use USB and LSB (without ECSS) to check this with zero beat.

- 3. Connect a DC voltmeter to TP4 of the ECSS unit CMF-78.

- 4. Set ECSS ON (USB or LSB) and check that the PLL locks; the voltage at TP4 should be anywhere at 4.5VDC if the ECSS was aligned prior acc. to the service manual.

- 5. Reduce the input level of the AM-signal and observe the point, where the PLL loses synchronism and the ECSS starts howling.

- 6. Readjust RV1 on the ECSS Unit for synchronism again.

- 7. Repeat 5) and 6) until the input level is close to noise floor and synchronism can still be achieved.

- 8. Change between ECSS/USB and ECSS/LSB to see, that synchronism is symmetrical for both sidebands even for weak signals close to the noise floor.

- 9. Slowly(!) detune the 535(DG) into both directions until ECSS loses synchronism and check that this loss appears at app. the same frequency variation, e.g. +/- 500Hz.

- 10. Try to find the optimum at 5) to 9).

- 11. Measure the voltage at TP4, it should be a little bit higher than before I've measured 4.77VDC instead of 4.50VDC before.

With this alignment method, the ECSS in the 535(DG) should operate and maintain stability even with fading and weak signals much better.

Additional idea:

After some time of operation, I noticed that the stability of the alignment was better but wasn't as good as I had expected.

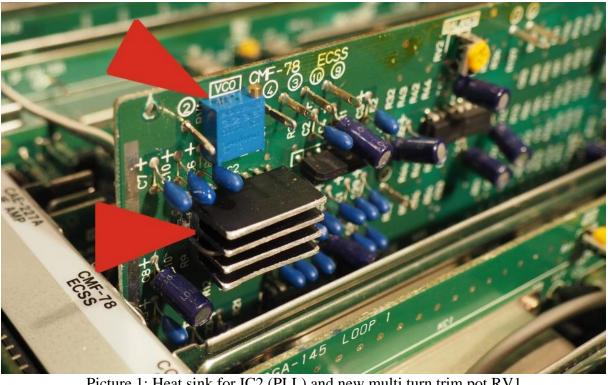

One reason is the thermal instability of the PLL-IC (IC2) MC14046, which has a power dissipation of app. 500mW(!) acc. to the data sheet. So it seems to be a good idea to use a small heat sink for DIP 16 ICs with a clip – see picture 1.

Picture 1: Heat sink for IC2 (PLL) and new multi turn trim pot RV1

Be careful with the clip, which has to be clipped under the IC, and avoid contact with the pcb and its wires. Had to cut the heat sink, because it was a little bit too high for the small space. A small drop of thermal grease will help. Hope this will increase the thermal stability. Additionally I replaced RV1 by a multi turn trim potentgiometer.

If you want to contact the author: Stefan Steger, DL7MAJ, eMail: stefan.steger@t-online.de Homepage: www.dl7maj.de